次世代トランジスタト構造GAAとパイオニア特許紹介

2022年11月11日、経済産業省は次世代半導体の製造基盤の確立に向けた研究開発プロジェクト(「ポスト5G情報通信システム基盤強化研究開発事業」における「②先端半導体製造技術の開発」)の採択先をRapidus株式会社(以下、ラピダス)に決定しました。

ラピダスはキオクシア、ソニーグループ、ソフトバンク、デンソー、トヨタ自動車、NEC、NTT、三菱UFG銀行の8社出資により新たに設立された会社で、日本初の最先端ロジック半導体のファウンダリビジネス立上げを目指しています。そのためにまず必要となるのが最先端の微細トランジスタ製造技術の確立です。

次世代トランジスタ構造GAA(Gate-All-Around)

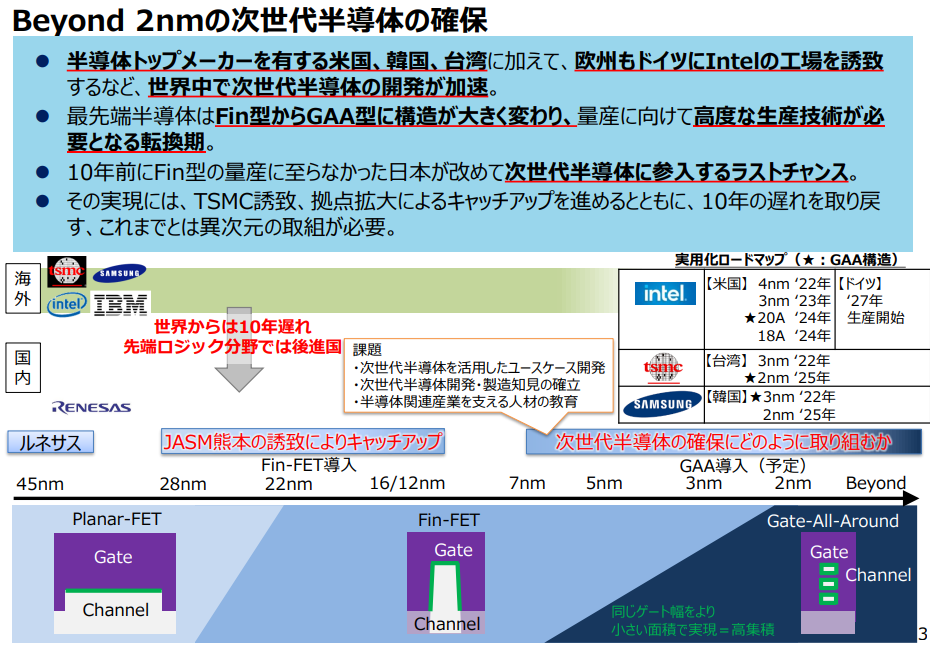

ラピダスが目指す2nm以降の最先端の微細半導体ではトランジスタ構造がFin-FETと呼ばれる構造からGAA(Gate-All-Around)と呼ばれる構造に大きく変わると想定されています。トランジスタ構造は22/28nm世代まではプレーナー型のMOSFET構造が用いられていましたが、16nm以降ではFin-FET型のMOSFET構造となり、そして2nm以降では横型のGAA型のMOSFET構造が採用される見込みです。

横型GAAはチャネル形状や材料などを最適し製造容易で且つ十分な性能を達成できるトランジスタの開発が大手半導体企業や研究機関で進められています。

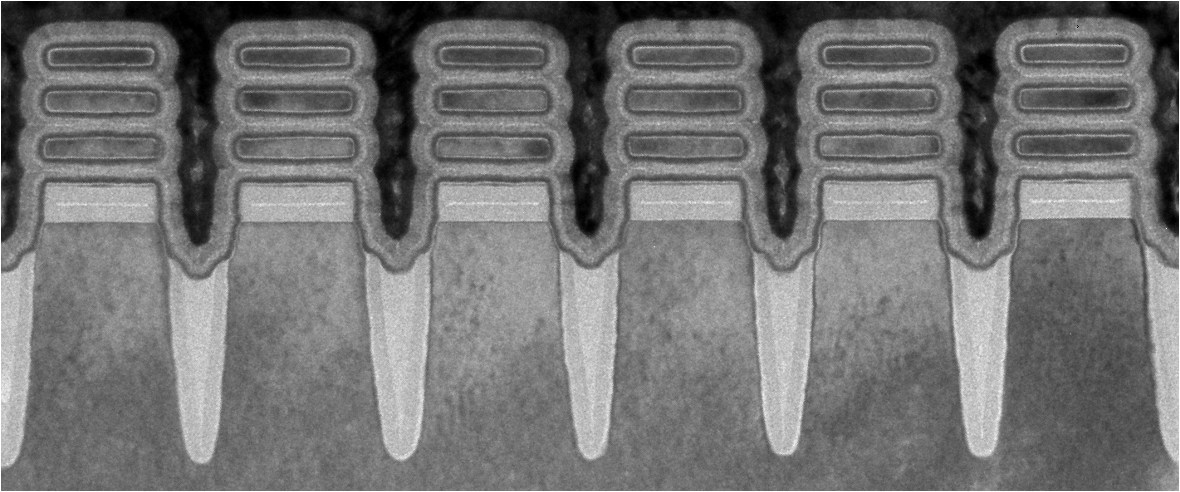

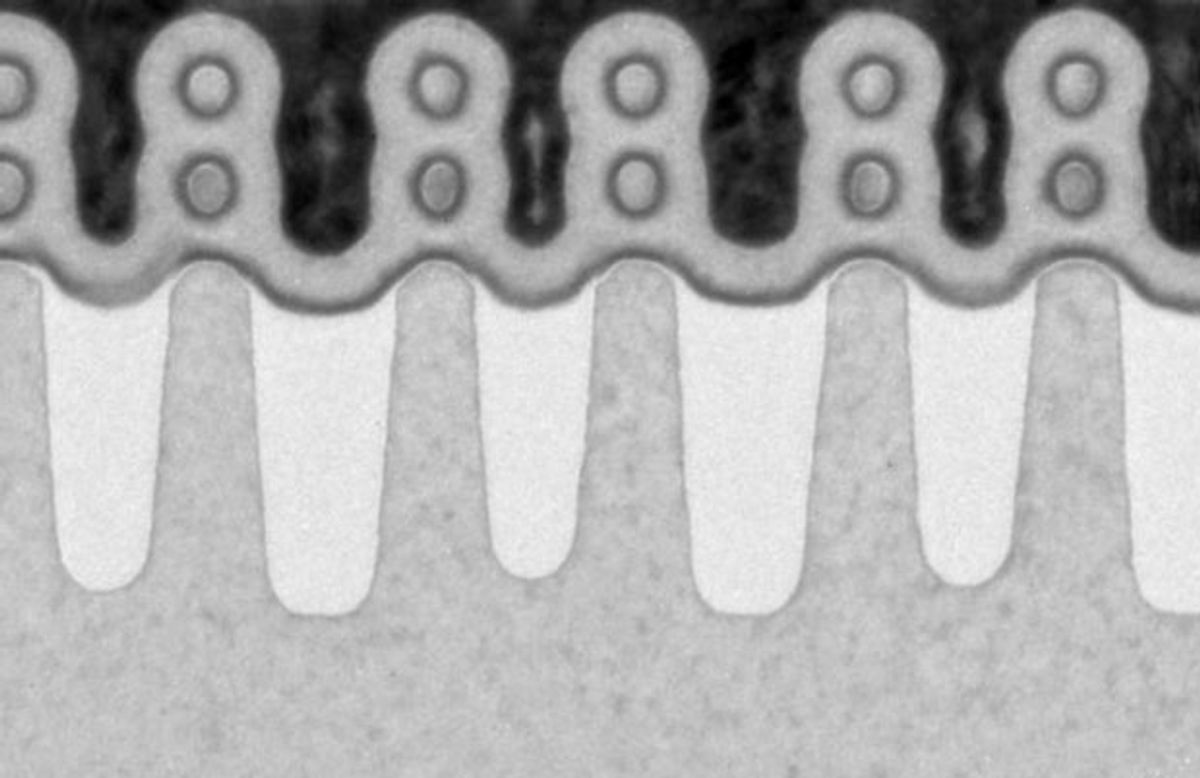

その横型GAA構造で有力なのがナノシート構造とナノワイヤー構造。違いはシリコンチャネル部分の構造でナノシートタイプはチャネル部分が平坦なシート構造であるのに対して、ナノワイヤータイプはチューブ構造となっています。ラピダスの連携先として考えられている米国IBM社が開発する最先端トランジスタ構造もナノシート型のGAA。複数のシート状のチャネル領域を上下並べ、それぞれのチャネル領域の周囲をゲートで囲む構造となってます。またサムスンが3nmプロセスとして導入したMulti-Bridge-Channel FET (MBCFET)と呼ぶ構造もナノシート構造のGAA。今後の主流はナノシート構造と考えられています。

トランジスタ構造のパイオニア特許紹介

すでに述べたように先端ロジック半導体のトランジスタの構造はプレーナー型に始まり、Fin-FET型を経てGAA型に移行しようとしています。今回はこの変遷の中で生まれてきたトランジスタ構造に関するパイオニア特許を紹介したいと思います。

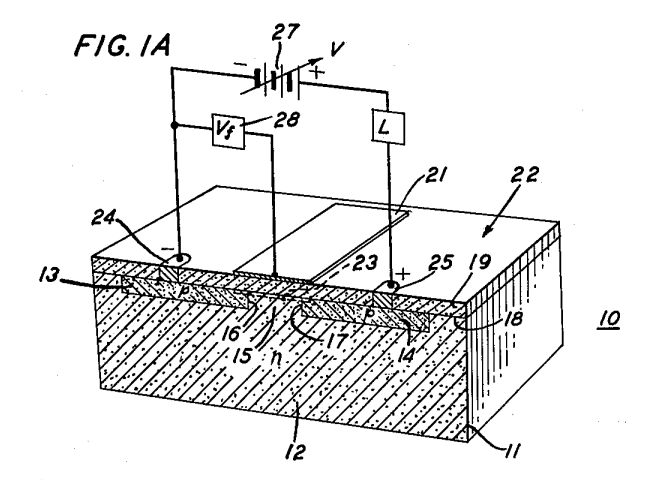

まず最初の世代のプレーナー型MOSFETトランジスタ。プレーナー型はチャネル領域が半導体基板表面に形成されていることからそのように呼ばれています。この構造は1959年にベル電話研究所の D.カーンと M.M.アタラによって発明されています。しかしながら最初の特許出願はそれぞれ別個に行われています。

まず最初に出願したのはアタラで、1960年3月8日にSer. No. 13,688として米国に出願され、1965年9月14日に米国特許3,206,670号として特許されています。一方、カーンの方はアタラより若干遅れて1960年5月31日に米国に出願(Ser. No. 32.801)を行い、1963年8月27日に米国特許3,102,230号として特許を受けています。

カーンとアタラの提唱したこの構造は一部は後述するFin-FET型に置き換えられたものの、依然としても現在でも多くの半導体集積回路に用いられており半導体デバイス関連の発明の中でも最もインパクトの大きいものの一つに挙げられています。

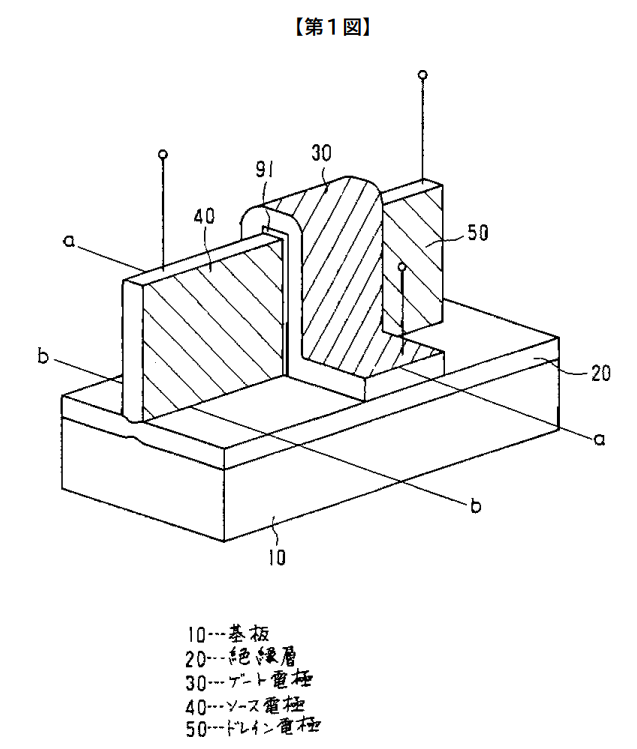

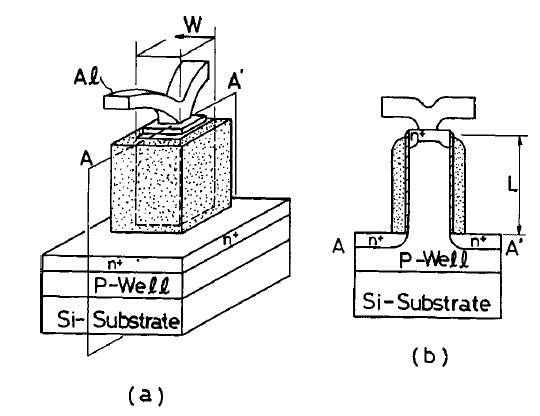

次はFin-FET構造です。1989年の国際電子デバイス会議(IEDM)で日立製作所の研究グループによって提唱されたDELTAトランジスタが最初のFin-FET構造のトランジスタと言われています。このDELTAトランジスタに関して日立製作所は1988年11月21日に日本に特許出願(特願昭63-292499)を行い、その後1989年2月28日にこの出願を優先権主張の基礎とする出願(特願平1-045403)を行い、1998年4月10日に特許2768719号として特許を受けています。その後、Fin-FET構造は2011年にIntelの22nmプロセスで初めて量産導入されました。

なお、日立製作所の特許出願の審査過程で引用された先行文献(特開平1-8670,特開平64-27270)でもFin状のチャネル領域の三方をゲート電極で囲った構造が開示されています。

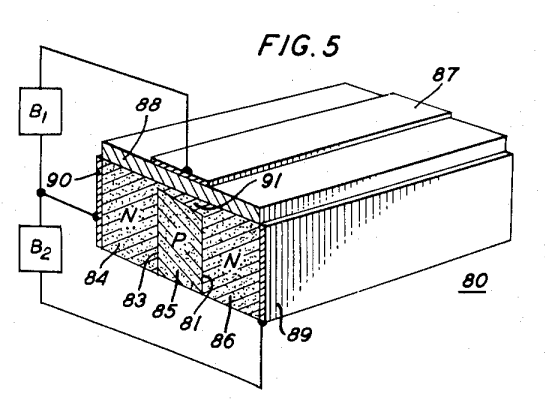

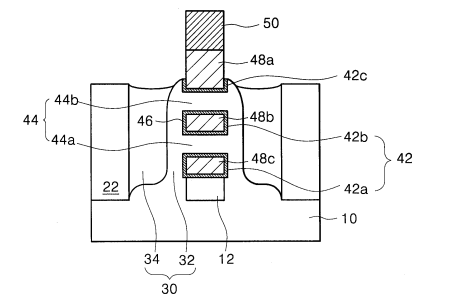

最後にGAA構造です。GAA構造のは1988年に東芝の研究グループによってSurrounding Gate Transistor(SGT)という名称で提唱され、IEEE Transactions on Electron Devicesで報告されています。発明者にはフラッシュメモリの発明者として舛岡富士夫氏が含まれています。このSGT構造に関して東芝は1988年9月6日に日本に特許出願(特願昭63-223008)を行い、1998年4月10日に特許3057661号として特許を受けています。この東芝の発明はチャネルを垂直方向に形成するいわゆる縦型GAAとです。縦型GAAは3次元NANDフラシュメモリのメモリセルとしてすでに実用化されてはいますが、まだCMOS回路を構成する先端微細半導体プロセスでは実用化はされておらず横型GAAの後の技術と考えられています。

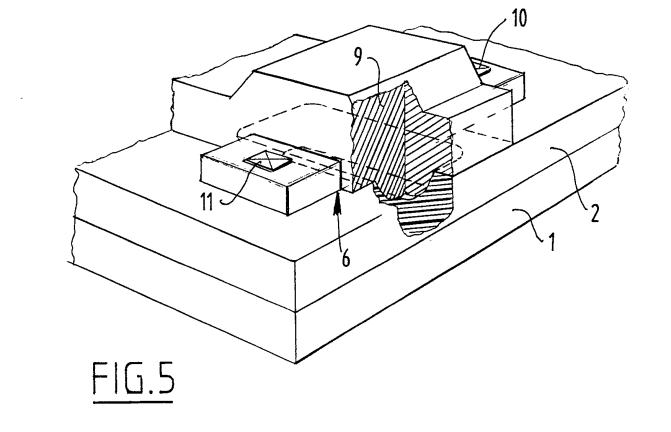

一方、横型GAAの特許出願は1989年頃から存在が確認できます。横型GAAに関する初期の特許出願の一つがIMEC(Interuniversity Microelectronics Centre)によって1989年9月21日に行われたオランダ出願(NL8902372A)です。この発明ではSIMOX(Separation by Implanted Oxygen)と呼ばれる製法でシリコン基板(1)と分離して形成されたシリコンチャンネル膜の直下のシリコン酸化膜(2)に開口部を設け、その開口部を利用してゲート電極でシリコンチャネル膜を囲む構造を採っており、現在主流になると想定されているナノシートやナノワイヤーの構造とはかなり異なっています。ナノシート構造やナノワイヤー構造の出願は2002年頃から存在を確認できます。

KR100481209B1 図2.b

US6583014B1 Fig.3